RS232 Signalanalyse mit einem Logikanalysator

RS232 wurde bereits in den 1960ern eingeführt und standardisiert. Die RS232 Schnittstelle ist hardwaremäßig und softwaremäßig sehr einfach gestaltet. Daher ist sie auch in einfacheren Umgebungen, z.B. bei Microcontroller-Anwendungen, gut einzusetzen.

Hier soll exemplarisch die Analyse des RS232 Signals eines PC-Motherboards mit einem Logikanalysator dargestellt werden. (Eigentlich möchte ich nur meinen neu erstandenen kleinen Thurlby-Logikanalysator testen und mache das an diesem Beispiel…). Außerdem wurde dasselbe mit einem Oszilloskop gemacht.

Spannungspegel

Auf den Leitungen des RS232 Kabels wird mit Spannungen von -12 V für einen High-Pegel und +12 V für einen Low Pegel gearbeitet, es kommt also negative Logik zum Einsatz. Spannungen unter -3 V werden als Low gewertet, und Spannungen über +3 V werden als High gewertet. Die Umsetzung von TTL-Pegeln auf RS232 Pegeln erfolgt mit Bausteinen wie MAX232. Datenleitungen liegen im Ruhezustand auf High.

PC-Schnittstellen benötigen aber im Allgemeinen die genannten Pegel (+/- 12 V) nicht. Meist kann man auch mit TTL-Pegeln arbeiten, wenn diese nur invertiert ( in negative Logik überführt) werden. Dann gilt 0 Volt als High, 5 Volt als Low.

Kabelbelegung

Die minimale Anzahl von Drähten für eine funktionierende RS 232 Verbindung besteht aus den folgenden Signalen:

- TxD des Senders an RxD des Empfängers (Pin 3 an Pin 2)

- RxD des Senders an TxD des Empfängers (Pin 2 an Pin 3)

- Gnd des Senders an Gnd des Empfängers (Pin 5 an Pin 5)

Es geht auch komplexer, mit Handshake-Leitungen, ist im Mikrocontrollerbereich aber nicht attraktiv, da dann mehr Port-Leitungen verwendet werden müssen.

Protokoll

Um mit der Minimalbelegung eine stabile Verbindung ohne Datenverlust zu realisieren, wird üblicherweise ein Software-Protokoll eingesetzt. Mittels der über die Leitungen gesendeten Signale XOFF und XON wird das Gegenüber zum Stoppen bzw. Fortsetzen der Datenübertragung aufgefordert. Wenn beide Seiten aber schnell genug sind, kann auch hierauf verzichtet werden.

Bytes werden bitweise sequentiell übertragen, LSB zuerst, MSB zuletzt. Sender und Empfänger müssen auf die gleiche Baudrate eingestellt werden, möglich sind Werte zwischen 300 Baud und mehr als 100 KBaud. Mangels Takt wird der Beginn eines Bytes fest mit einem Low angezeigt, dem Startbit. Dem Ende des Bytes folgt ein Stopbit, das immer High ist. Neben der Baudrate und der Anzahl der Stopbits (0,1,2) kann auch noch ein Parity-Bit übertragen werden. Die einzelnen Bits passen in das durch die Baudrate vorgegebene Raster. Zusammengefasst also die folgenden Eigenschaften:

- Ein Startbit (Low)

- Datenbyte: LSB zuerst, MSB als letztes (also: Bit 0, Bit 1, … Bit 7)

- mindestens 1 Stopbit (High)

Im folgenden wird ein konkretes Signal analysiert. Das Signal wird am USART-Ausgang des Microcontrollers ATmega8 abgegriffen, besitzt also noch TTL Pegel und positive Logik.

Das Signal ist auf 19200 Baud eingestellt. Desweiteren ein Stopbit und kein Paritätsbit. Somit kommen auf ein Byte 10 übertragene Bit. Die Länge eines Bits berechnet sich t=1/f wobei f die Baudrate ist. Für 19200 Baud ergibt sich ein Wert von ca. 52 Mikrosekunden.

Analyse mit einem Oszilloskop

Oszilloskop Zeitablenkung wurde auf 100µs eingestellt. Dann passen etwa 2 Bits in eine Skaleneinheit. Dann wurde ein einzelner Buchstabe ‘a’ gesendet. Dieser entspricht hexadezimal 61h und 0110.0001 dual. Da die Bits LSB first gesendet werden, wird ein Bitmuster …1000.0110… erwartet.

Buchstabe ‘a’. Gemessen an einem AVR der mit

3,3Volt betrieben wird.

Buchstabe ‘a’. Gemessen an einem AVR der mit

3,3Volt betrieben wird.

Oben sieht man das Startbit (Low), ein High Bit, 4 Low-Bits, 2 High Bits, 1 Low Bit und den Übergang zurück nach High. Zusammngestellt also:

...111010000110111...

Fett dargestellt wurde die gesuchte Bitfolge “1000.0110”. Dies ist unser ‘a’ mit LSB first. Die ‘0’ davor ist das Startbit, die ‘1’ danach das Stopbit.

Insgesamt also genau das erwartete Ergebnis.

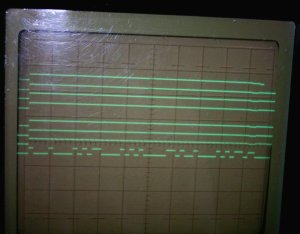

Analyse mit einem Logikanalysator

Der Logikanalysator wird auf 100 Mikrosekunden Periodenlänge eingestellt. Er wird an RxD, TxD und Gnd angeschlossen. Ein Testprogramm gibt kontinuierlich eine Zeichenfolge („ABC”) auf TxD aus.

Oben Logikanalysator, unten

Oszilloskop (Der abgebildete Logikananlysator gibt sein Videobild über einen

Oszilloskop aus)

Oben Logikanalysator, unten

Oszilloskop (Der abgebildete Logikananlysator gibt sein Videobild über einen

Oszilloskop aus)

Der Logikanalysator wird gestartet und nach kurzem unterbrochen. Sein Speicher ist nun voll mit den Signalen der Schnittstelle. Eine Übertragung der High/Low Pegel in eine Eins-Null-Folge bringt folgendes Ergebnis, das aus dem Analysatorspeicher wahllos herausgegriffen wird:

10 0 01000010 1 0 110000101 0100000110 10010000101 011000101 0100000101

0010000101 0110000100101000

Die gewählte Gruppierung erfolgte beliebig.

Die Buchstaben A, B und C sehen als Bitmuster inklusive Start/Stopbit wie folgt aus:

Hex Bitmuster mit LSB zuerst

A 41 0 1000 0010 1

B 42 0 0100 0010 1

C 43 0 1100 0010 1

Der Vergleich der Bitmuster mit dem Ausschnitt aus dem Analysatorspeicher ergibt folgendes:

....10

0 0100.0010 1 = B

0 1100.0010 1 = C

0 1000.0011 01 = A das zweite High dauert länger

0 0100.0010 1 = B

0 1100.010 1 = C das dritte High dauert zu kurz

0 1000.0010 1 = A

0 0100.0010 1 = B

0 1100.00100 1 = C das 6. Low dauert länger

01000...

Man kann erkennen, dass die Daten nicht perfekt geliefert werden, sondern leichte Variation haben. Pegel dauern etwas zu lange oder etwas zu kurz. Das bügeln die Schnittstellenbausteine aber normalerweise aus. Bei Experimenten zwischen AVR Controller und PC konnten Zeichen durchaus auch dann noch in Teilen richtig übertragen werden, wenn die Baudrate falsch eingestellt war.

Das Lesen der Pegel erfolgt durch die Schnittstellenbausteine genau in der Mitte eines Bits, diese Mitte kann aber der Logikanalysator nicht anzeigen. Es gibt somit auch eine Ableseungenauigkeit am Logikanalysator.

Abgebildet sind 8 Dateninputs des Analysators,

mit dem Signal ist nur der untere Eingang belegt

Abgebildet sind 8 Dateninputs des Analysators,

mit dem Signal ist nur der untere Eingang belegt

Ergebnis

Insgesamt zeigt der Analysator das erwartete Ergebnis und mit etwas Mühe kann ein RS232 Strom nach Aufnahme durch den Logikanalysator „per Hand” analysiert werden. Auch Detailbetrachtungen mit dem Oszilloskop sind einfach möglich. Da die Speicherdaten aus dem Analysator in einen PC übertragen werden können, kann die Analyse dort automatisiert fortgesetzt werden.