Der Logik-Analysator Tektronix 1241

Geräte dieser Art waren in Forschung und Entwicklung der 80ger Jahre, besonders Entwurf von Logikschaltungen, sehr verbreitet.

Der Tek 1241 bietet bis zu 72 Kanäle, 2 Zeitbasen, einen farbigen Touchscreen und eine Bandbreite von 100 Mhz synchron und 50 Mhz asynchron. Er hat zusätzliche Slots für RAM- und ROM-Bausteine sowie für ein GPIB oder RS232-Interface. Er kann eine Tiefe zwischen 257 Bit (Aquisition mit Glitches mit einer Karte) und 4x512+1=2049 Bit analysieren (Acqisition ohne Glitches mit 4 Karten)

Mein Gerät hat ein 64KByte RAM-Baustein 12RS02, 2x9+2x18=54 Kanäle und zunächst leider kein GPIB-Interface. Dies habe ich später nachgekauft, leider war es zunächst defekt. Hier die Beschreibung der Reparatur des GPIB COMMPACKS 1200C02 .

Beim Gerät sind 6 Pods (Probes) vom Typ 6460 dabei. Dies sind Probes mit " Variable Thresholds", d.h. die zu verwendenden Werte für HI und LO können bei diesen Probes vom 1241 aus bequem eingestellt werden, Wertebereich -6.35..+6.35 V.

Handbücher zum Gerät sind im Internet zu finden.

Unterschiede 1240 und 1241: 1241 bietet ein farbiges Display. Die Geräte sind ansonsten wohl praktisch gleich, was ich daraus ableite, dass beide Typen dieselbe Firmware nutzen.

Glitches: Glitches sind kurzzeitige Signalunstabilitäten. Ein Signal, dass " eigentlich" logisch 1 ist, kann -wegen Signallaufzeiten in beteiligten Gattern o.ä.- für sehr kurze Zeit auf logisch 0 gehen. Dieses Verhalten ist sehr unangenehm, weil es in anderen Logikbausteinen, die dieses Signal aus Input besitzen, zu Zustandsänderungen kommen kann, die nicht gewünscht sind. Wenn das Störsignal deutlich kürzer ist als der Takt des Logik Analysators und so zwischen zwei Sample-Zeitpunkten liegt, sieht der Logik Analysator diese Zustandsänderung nicht und zeigt sie auch nicht an.

Um diese besondere Situation mit einem Logik Analysator dennoch zu unterstützen, besitzt der 1241 eine “Glitch Detection” Logik. Diese ist zwischen den Zeitpunkten aktiv, zu denen ein Sampling stattfindet. Die Logik prüft, ob eine Signaländerung zwischen den beiden Zeitpunkten stattgefunden hat (ohne das dies zu einem echten Signalübergang geführt hat). Wenn dies der Fall ist, wird der Übergang als Glitch im Diagramm dargestellt.

Der 1241 kann Glitches bis hinunter zu einer Länge von 6ns erkennen.

Demultiplexing: Auf einem Bus werden typischerweise zu verschiedenen Zeitpunkten verschiedene Arten von Daten transportiert: z.B. Daten und Adressen ( Multiplexing). Der 1241 ist in der Lage, bei entsprechender Konfiguration diese unterschiedlichen Datentypen wieder aufzutrennen und z.B. in verschiedenen Gruppen in zeitlich korrekter Reihenfolge darzustellen. Diesen Vorgang nennt man Demultiplexen und er erfordert die Nutzung zweier Zeitbasen.

Frontansicht

Bedienungselemente vorn

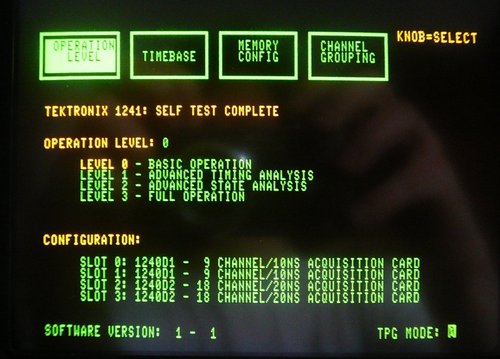

Dialog Operation Level: Es wird der aktuelle Level sowie die Slotbelegung angezeigt. In meinem Gerät sind zwei 9-Kanal und zwei 18-Kanal-Einschübe in den Slots. Das ist eine ziemlich gute Ausstattung.

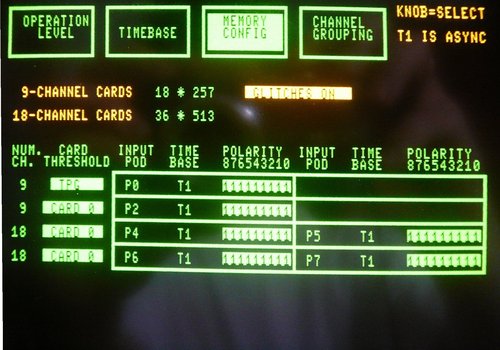

Dialog Memory Configuration. Hier wird pro Probe die zu nutzende Zeitbasis, der Trigger/Signal-Theshold etc. eingestellt.

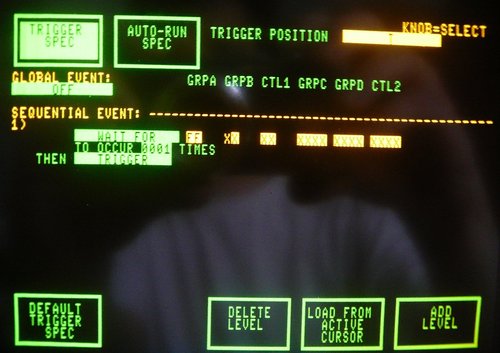

Dialog Trigger Specification. Hier wird auf das einmalige Auftreten des Wertes ' 0xff’ an der Probe 0 (GRPA) gewartet.

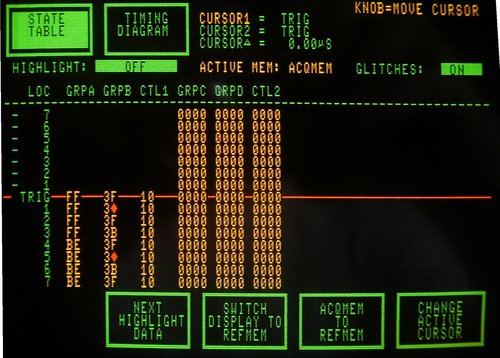

Ausgabe der State Table nach Start der Akquisition und Eintreten des Triggers. Die rote Linie(=CURSOR1) zeigt den Triggerzeitpunkt an. Die roten Rauten zeigen Glitches im Signal an.

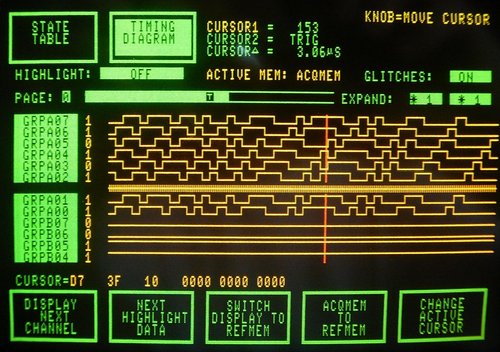

Ausgabe der State Table. Es wurde zum Zeitpunkt t=3,06 Mikrosekunden nach Triggerereignis gescrollt. Zu dem Zeitpunkt lag das Datenbyte ‘d7’ an.

Ausgabe des Timing Diagramms zum Zeitpunkt t=3,06 Mikrosekunden nach Triggerereignis. Es werden 12 Datenleitungen dargestellt.

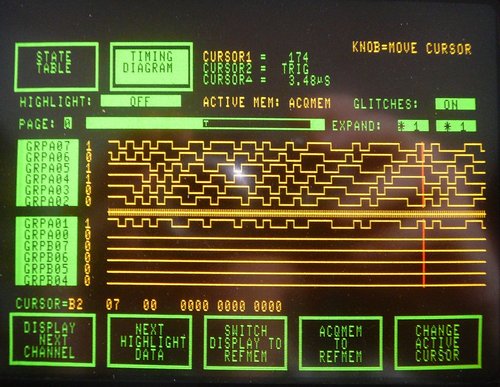

Ausgabe des Timing Diagramms zum Zeitpunkt t=3,48 Mikrosekunden nach Triggerereignis. Zu dem Zeitpunkt lag das Byte ‘b2’ an.

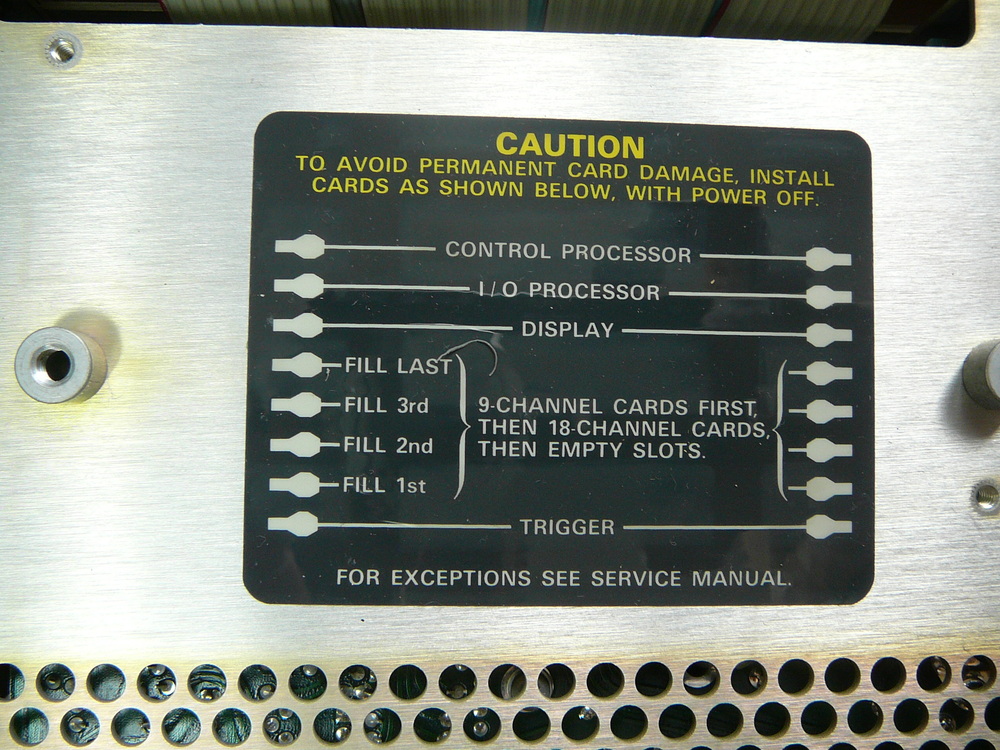

Die 4 Slots des Geräts. Ganz oben der Ausgang des

Testgenerators, unten das eingesteckte RAM Pack. Mittig die beiden 9-Kanal und

die beiden 18-Kanal-Karten.

Die 4 Slots des Geräts. Ganz oben der Ausgang des

Testgenerators, unten das eingesteckte RAM Pack. Mittig die beiden 9-Kanal und

die beiden 18-Kanal-Karten.

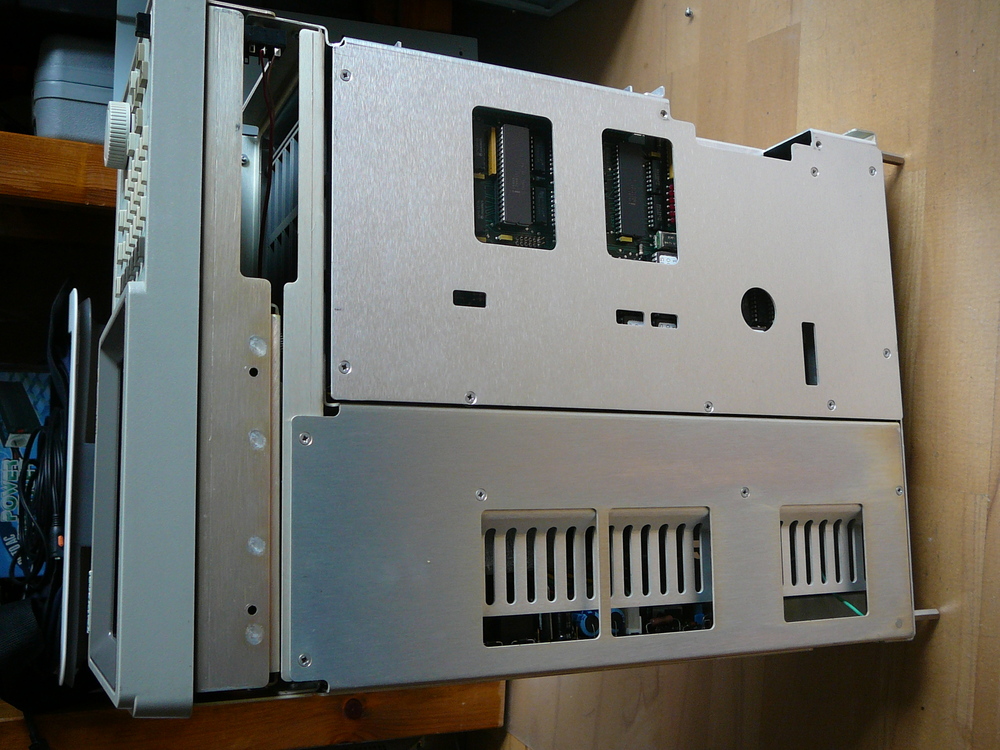

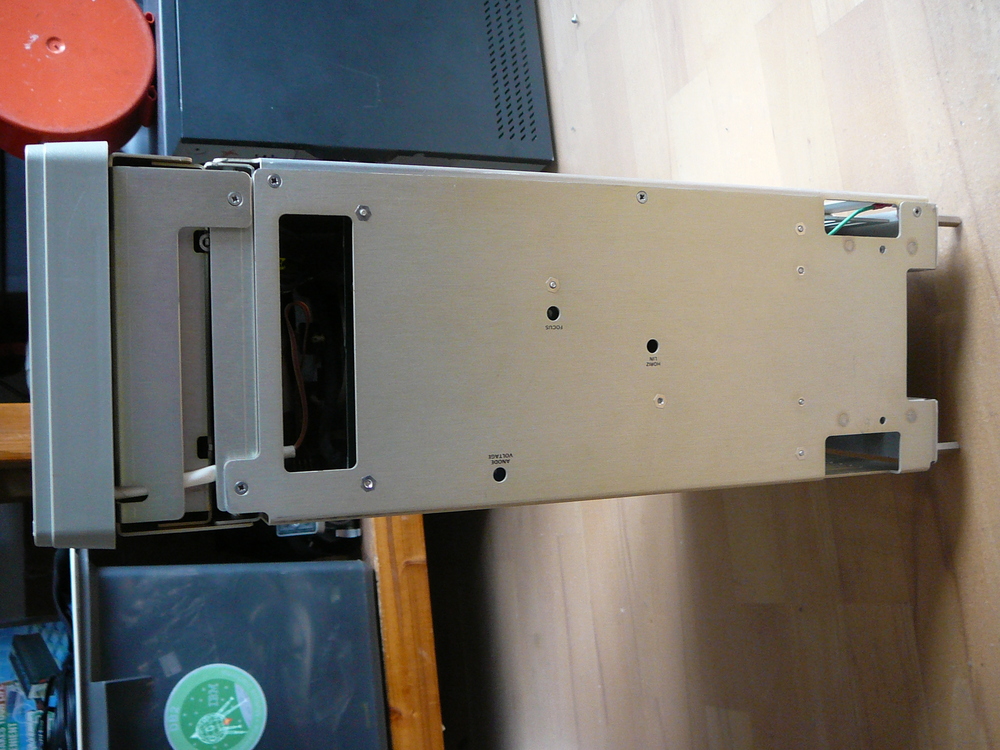

Ansicht von hinten. Ganz rechts das eingesteckte

GPIB Modul

Ansicht von hinten. Ganz rechts das eingesteckte

GPIB Modul

Trigger Aus- und Eingang.

Trigger Aus- und Eingang.

Innenansichten

Im folgenden einige Innenansichten des Geräts.

Auch ohne Gehäuse gibt sich der 1241 sehr

geschlossen :-)

Auch ohne Gehäuse gibt sich der 1241 sehr

geschlossen :-)

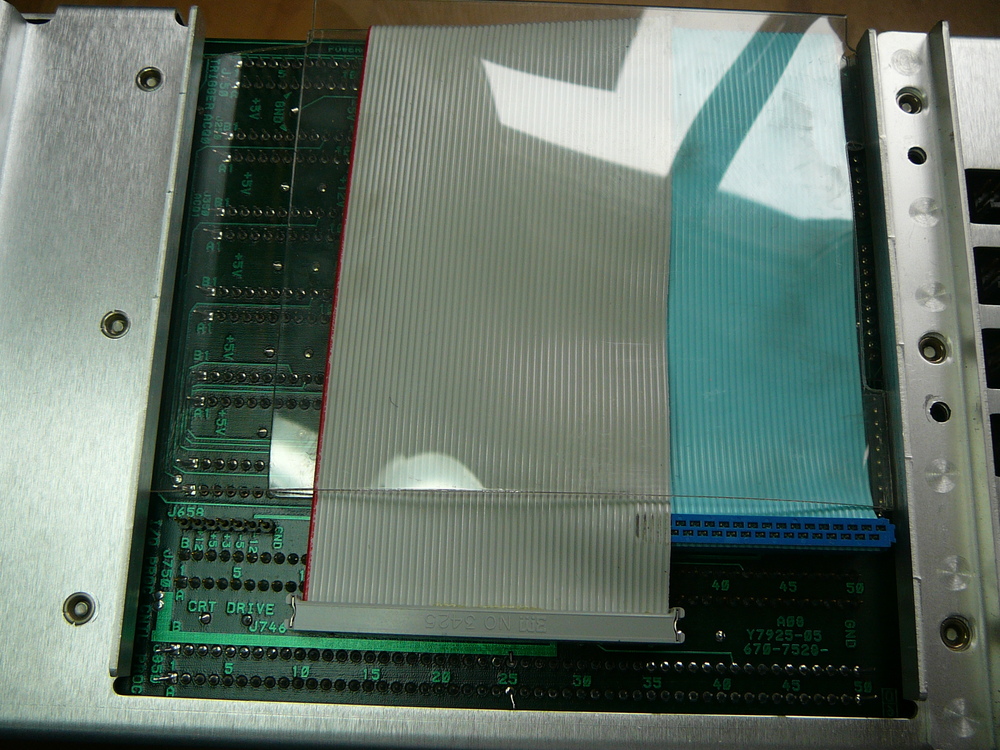

Im Inneren lässt sich ein an Scharnieren befestigter

kompletter Block -nach Lösen einiger Schrauben- herausklappen. In diesem Block

stecken alle Einsteckkarten des Geräts.

Im Inneren lässt sich ein an Scharnieren befestigter

kompletter Block -nach Lösen einiger Schrauben- herausklappen. In diesem Block

stecken alle Einsteckkarten des Geräts.

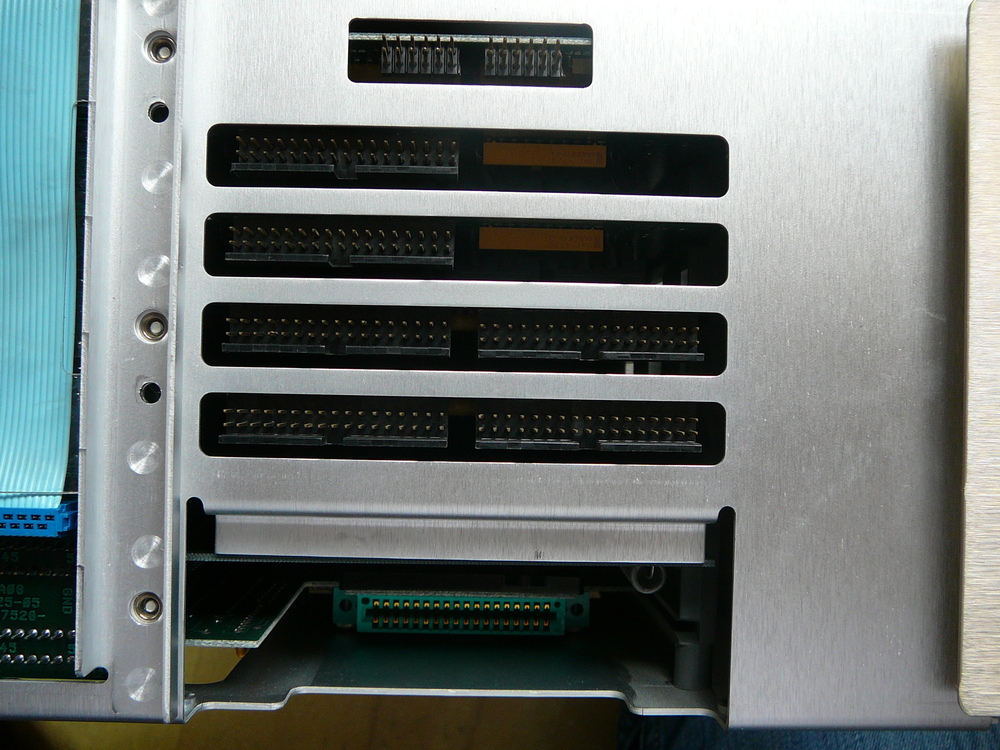

Blick auf die Karteneinschübe.

Blick auf die Karteneinschübe.

Im obigen Bild kann man von oben nach unten sehen:

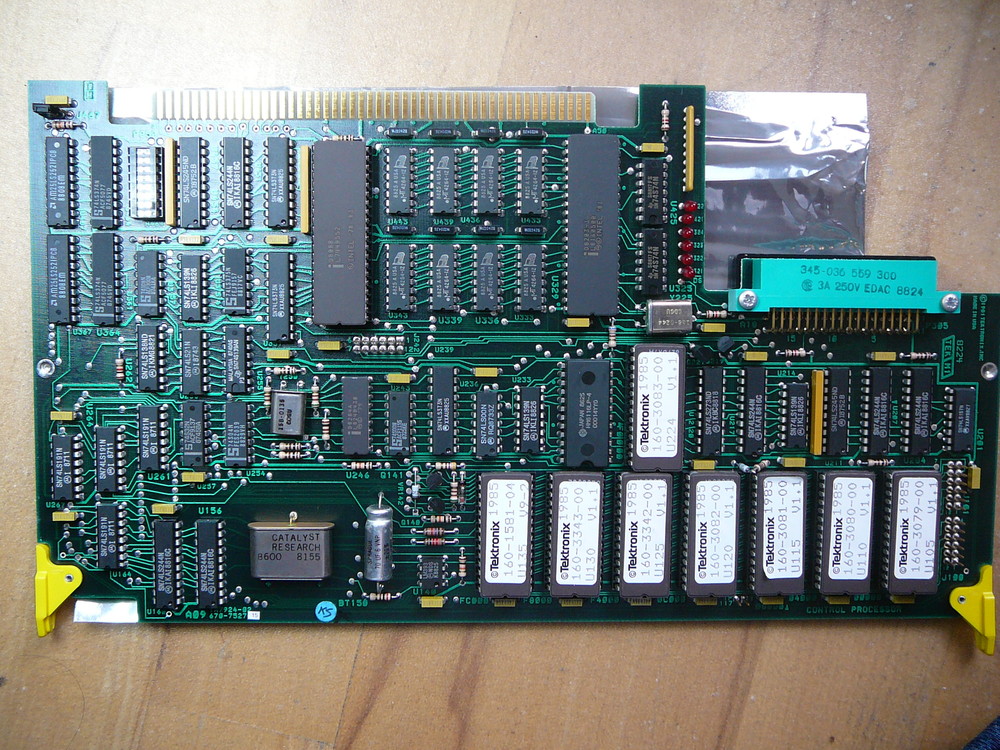

- Control Processor: Haupt-Prozessor Karte mit 8088

- I/O - processor: IO-Karte mit Z80

- Display: CRT-Karte

- 2x 9 Kanal Acquisition Karte

- 2x 18 Kanal Acquisition Karte

- Trigger Karte

Eine grobe Durchsicht der Produktionsdaten der Chips auf den Platinen zeigt, dass die neuesten Chips aus der 31. Woche von 1988 sind.

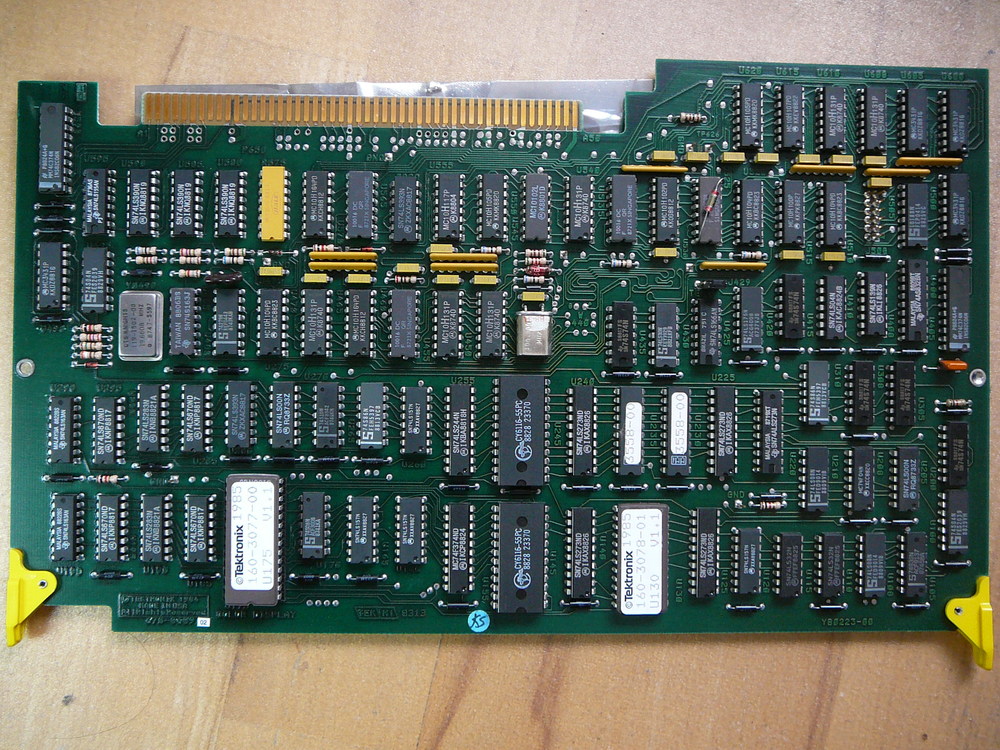

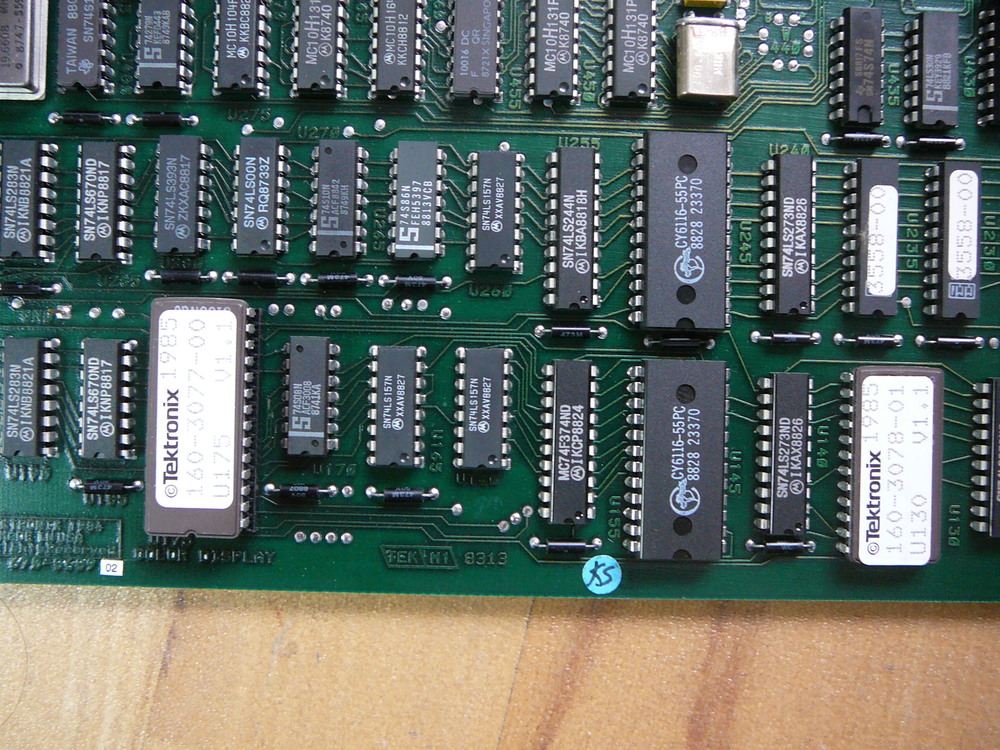

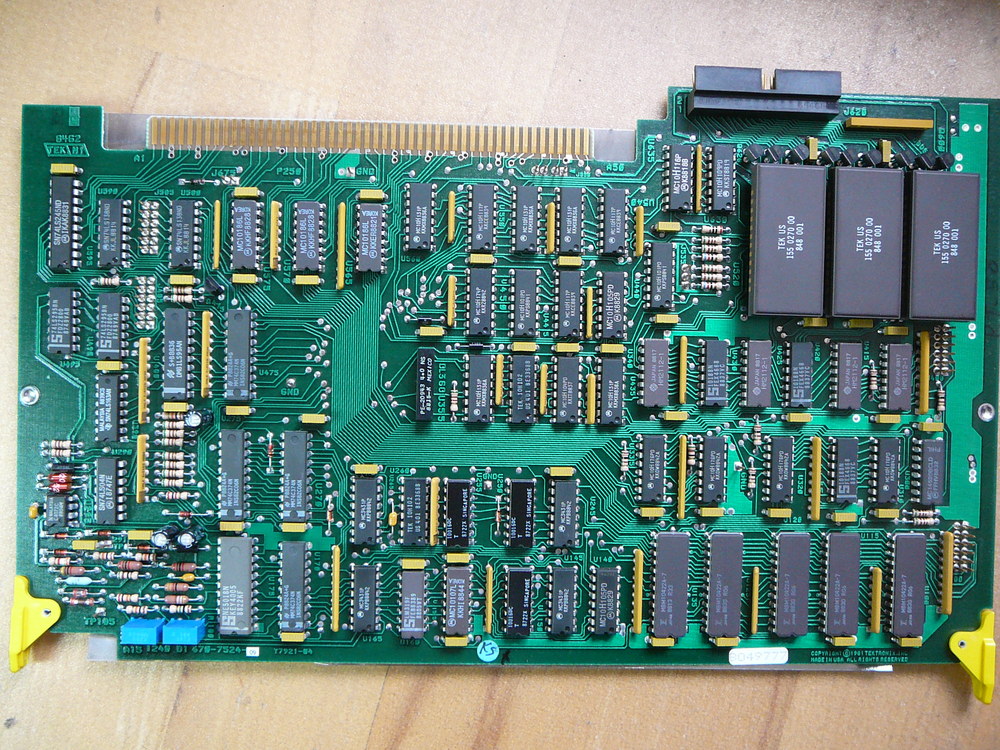

Prozessor Karte

Prozessor Karte

Prozessor Karte

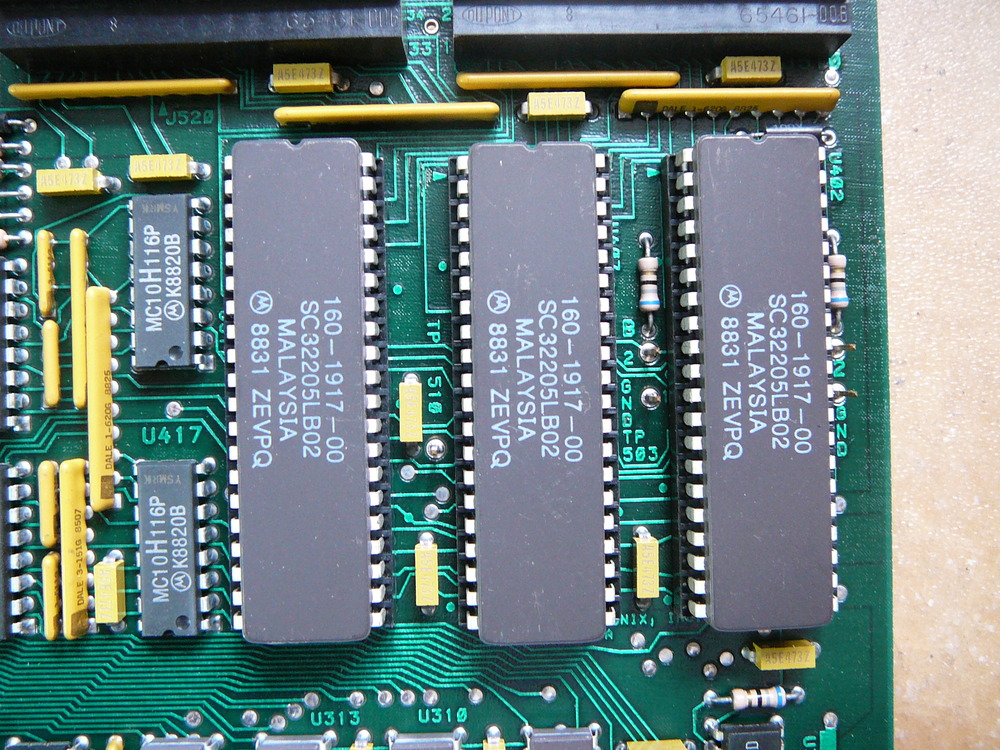

EPROMs auf Prozessor Karte

EPROMs auf Prozessor Karte

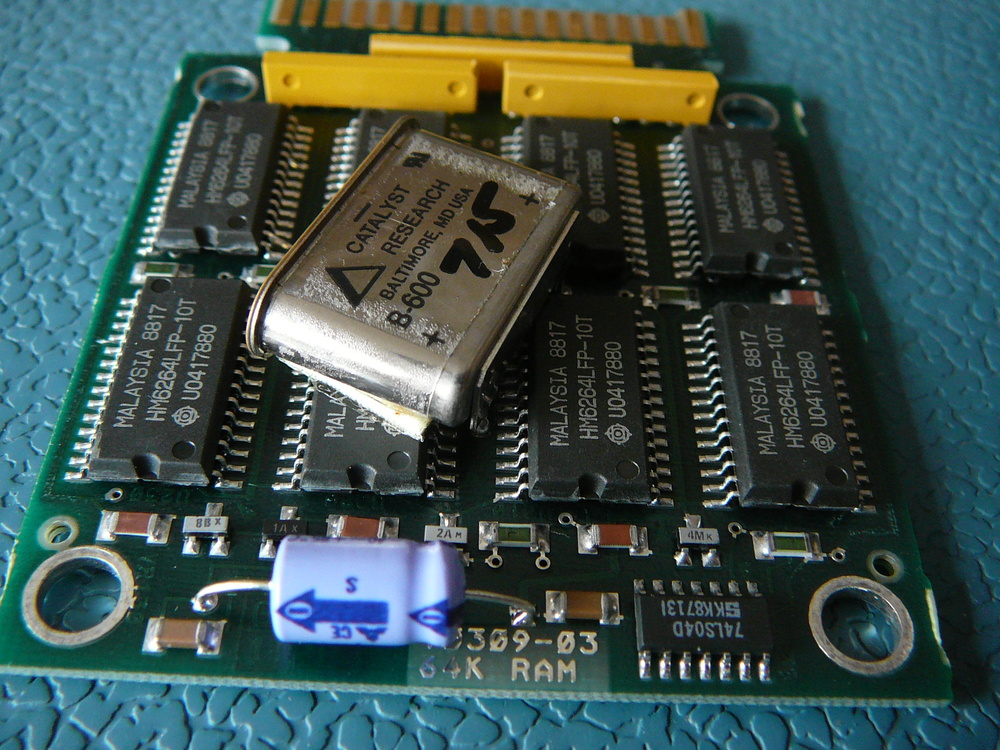

Die Batterie fürs Non Volatile RAM “Catalyst

Research. Solche langlebigen Batterien haben eine garantierte Haltbarkeit

typischerweise 30 Jahren. Mein Gerät ist von 1988, es würde also bis 2018

halten… Ein Ersatztyp für die “Catalyst Research B-600” (Lithium?, 2,8V?,

650mAh?) ist noch zu bestimmen

Die Batterie fürs Non Volatile RAM “Catalyst

Research. Solche langlebigen Batterien haben eine garantierte Haltbarkeit

typischerweise 30 Jahren. Mein Gerät ist von 1988, es würde also bis 2018

halten… Ein Ersatztyp für die “Catalyst Research B-600” (Lithium?, 2,8V?,

650mAh?) ist noch zu bestimmen

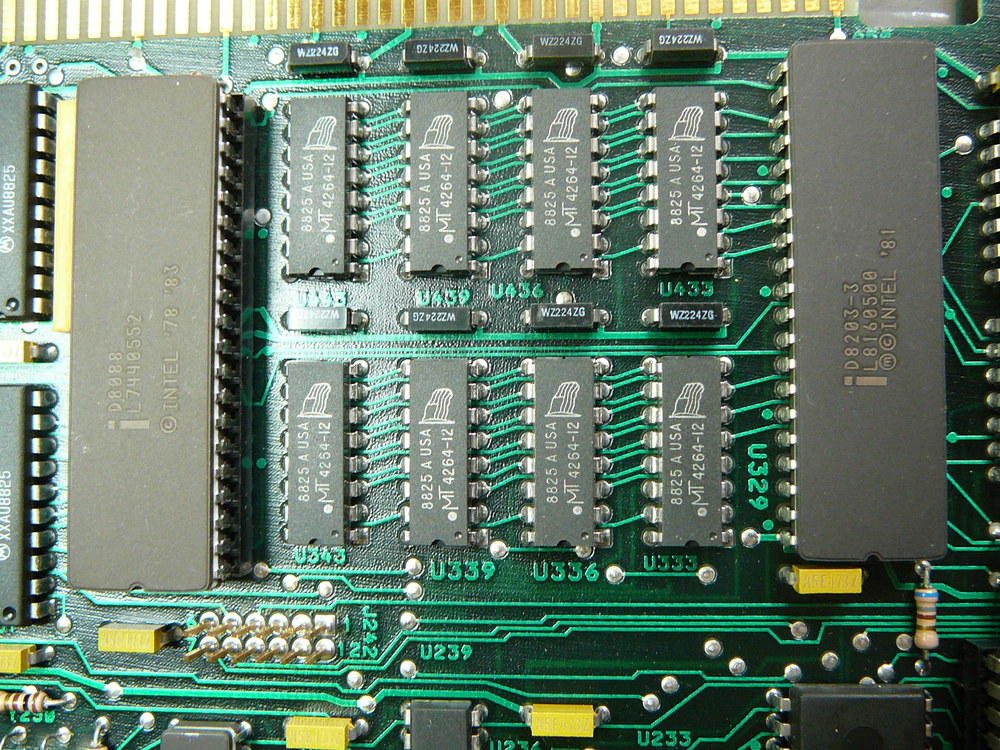

Der 8088

Der 8088

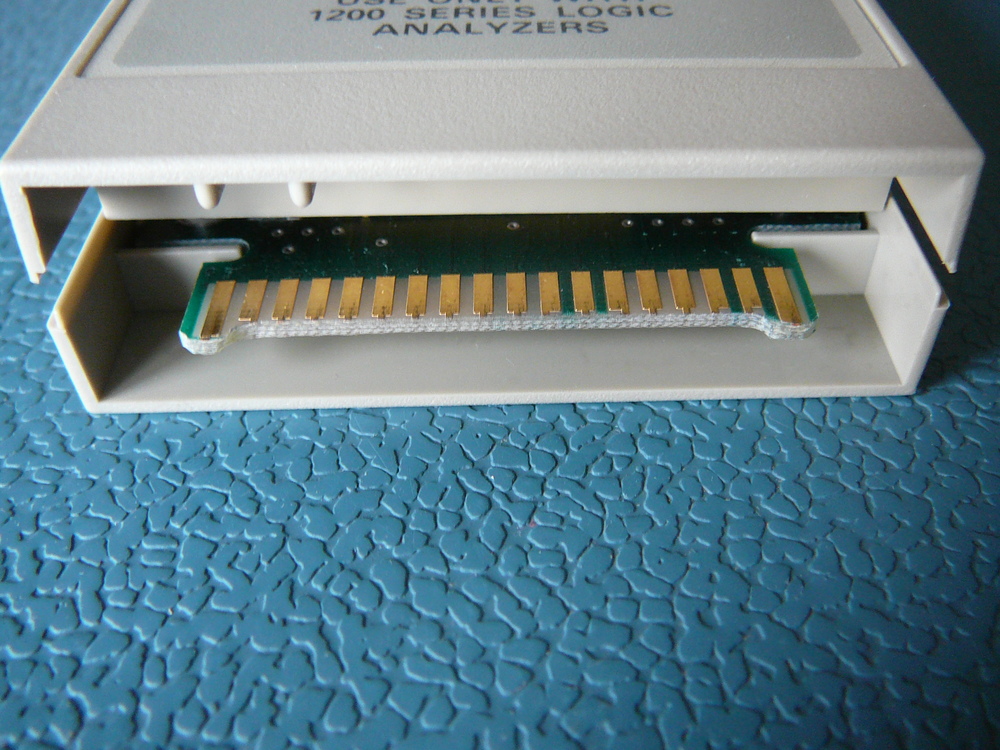

Aufnahmeplatz für RAM Pack

Aufnahmeplatz für RAM Pack

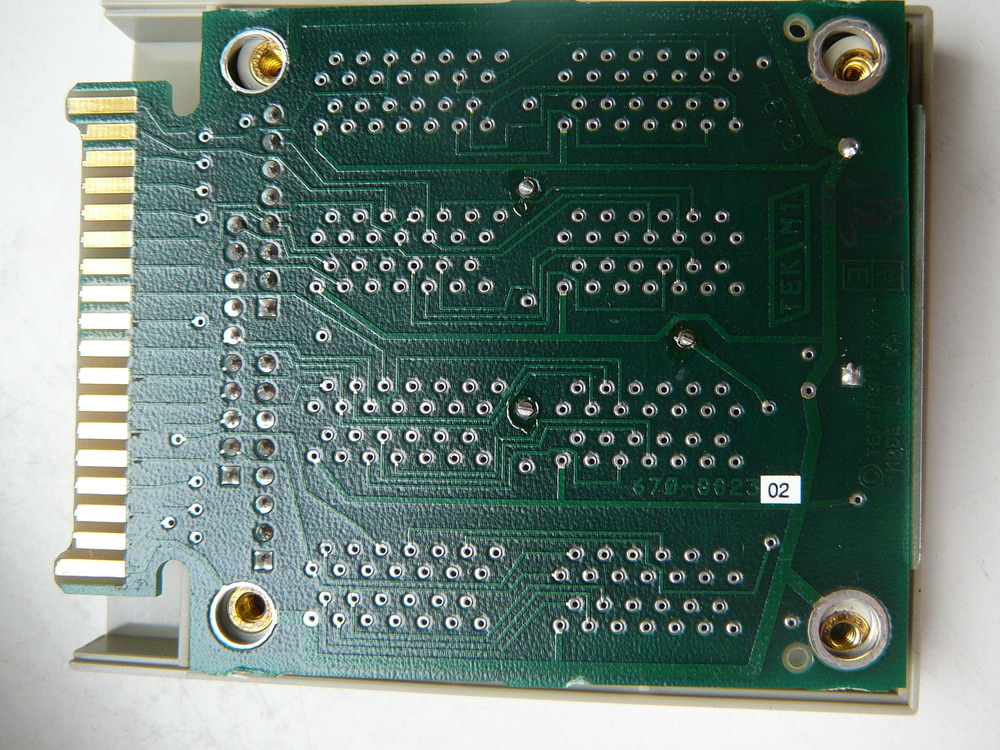

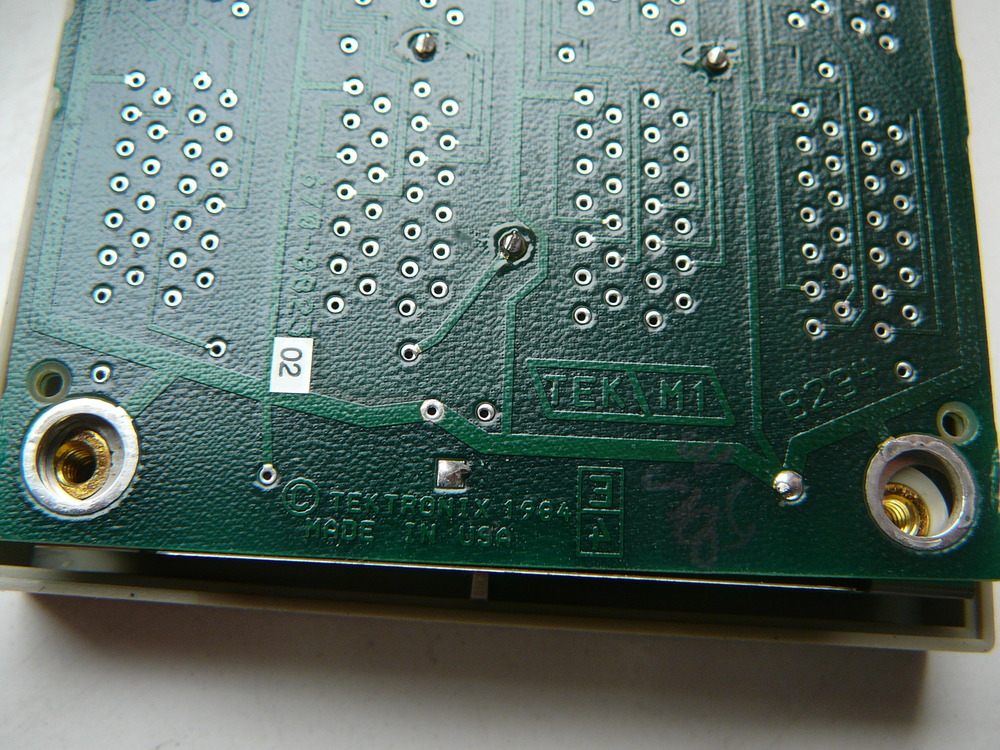

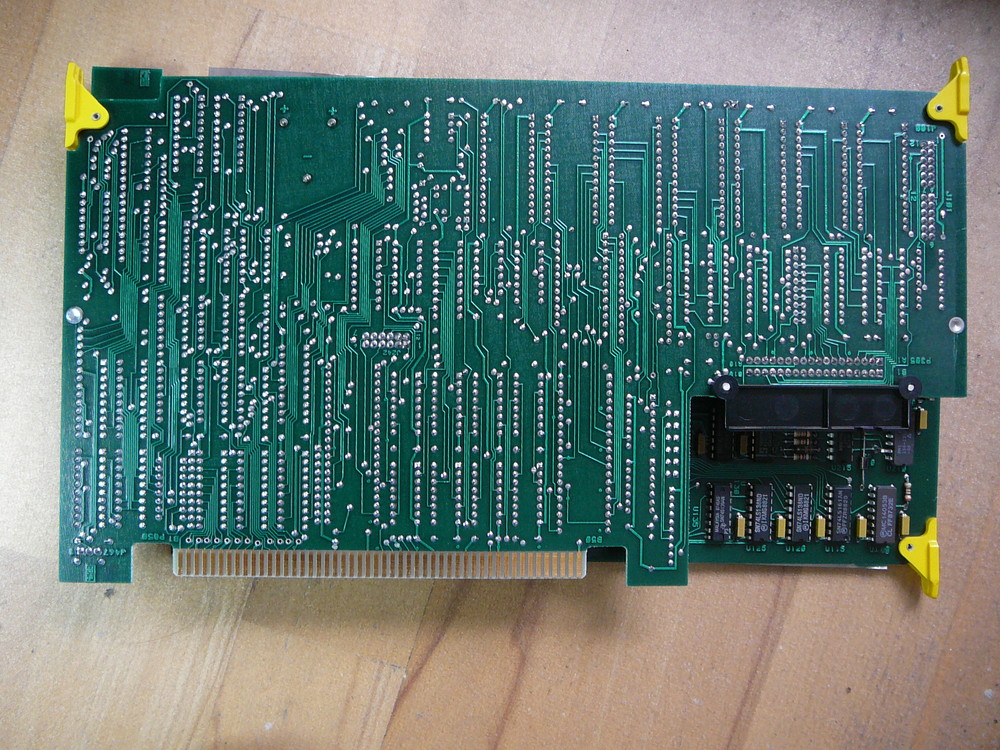

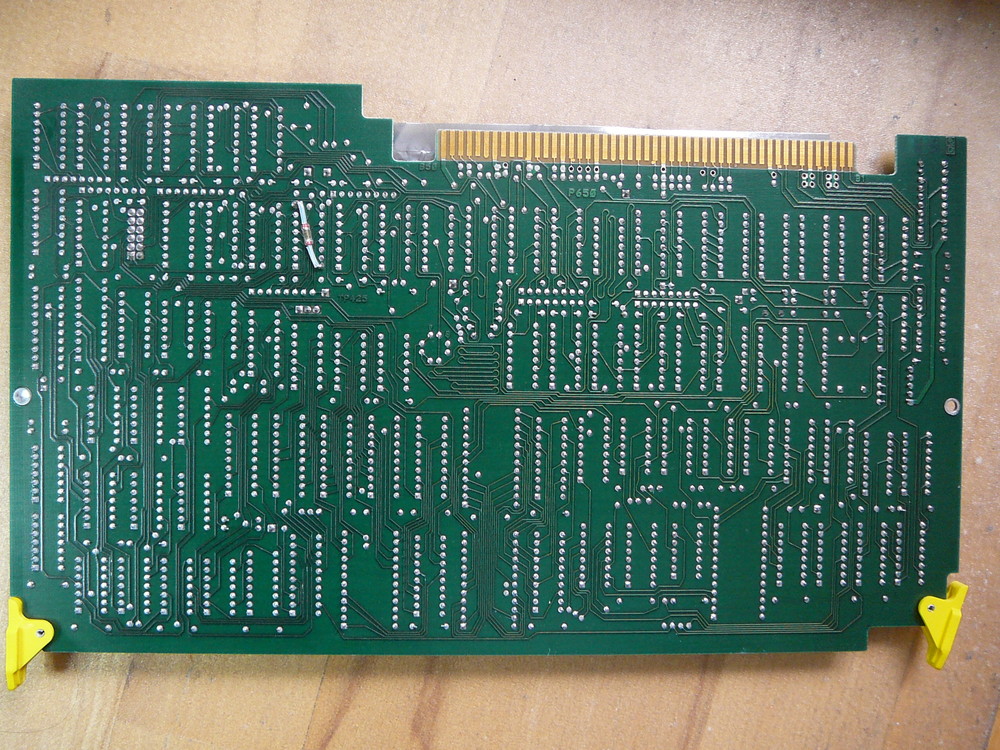

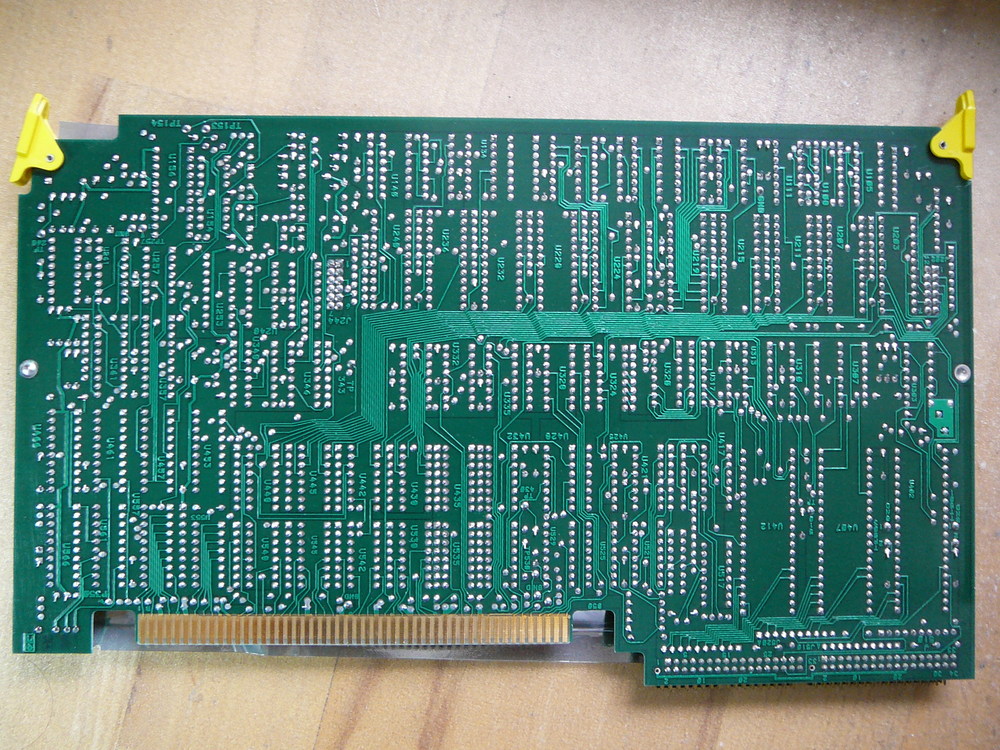

Unterseite Prozessor Karte

Unterseite Prozessor Karte

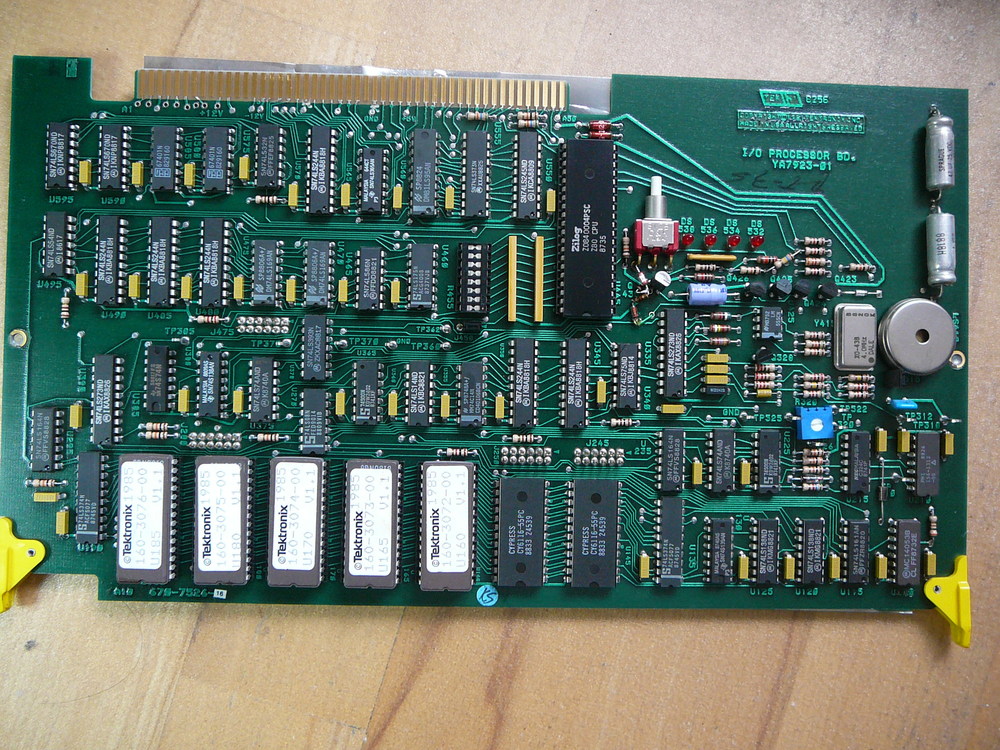

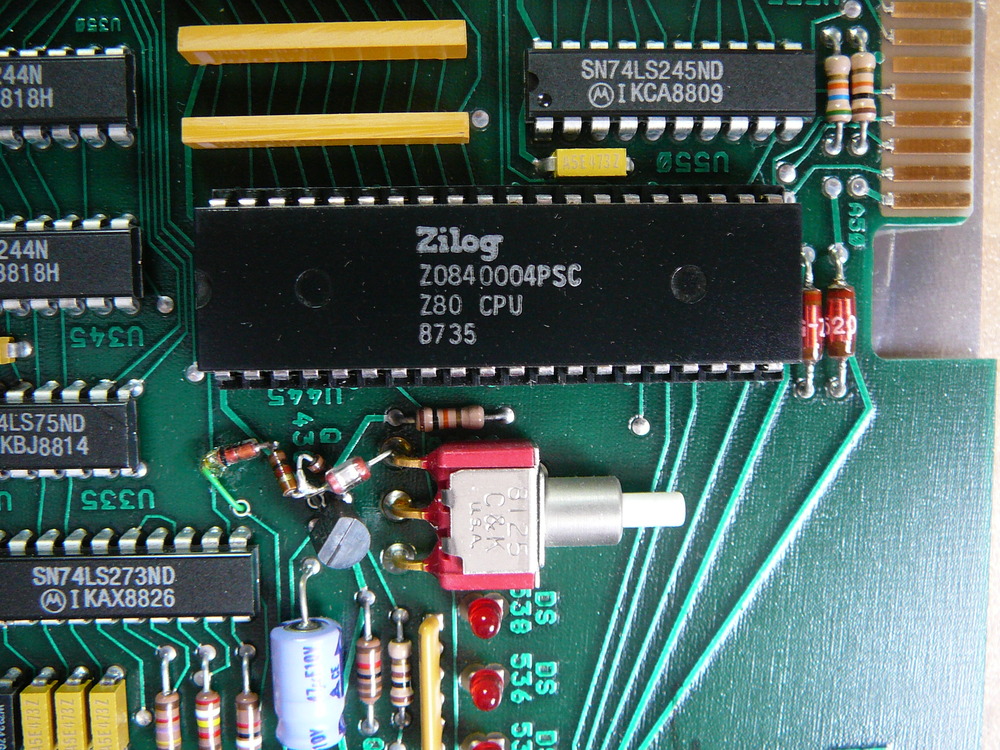

Die I/O Karte

Der Z80

Der Z80

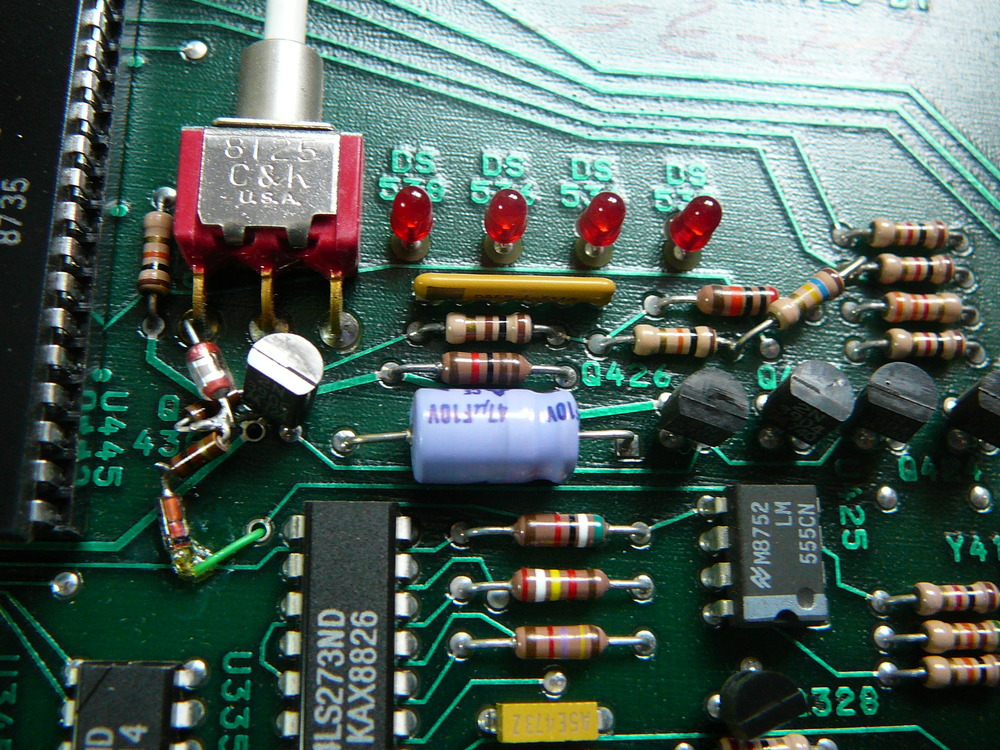

Schönes Handlöt-Detail

Schönes Handlöt-Detail

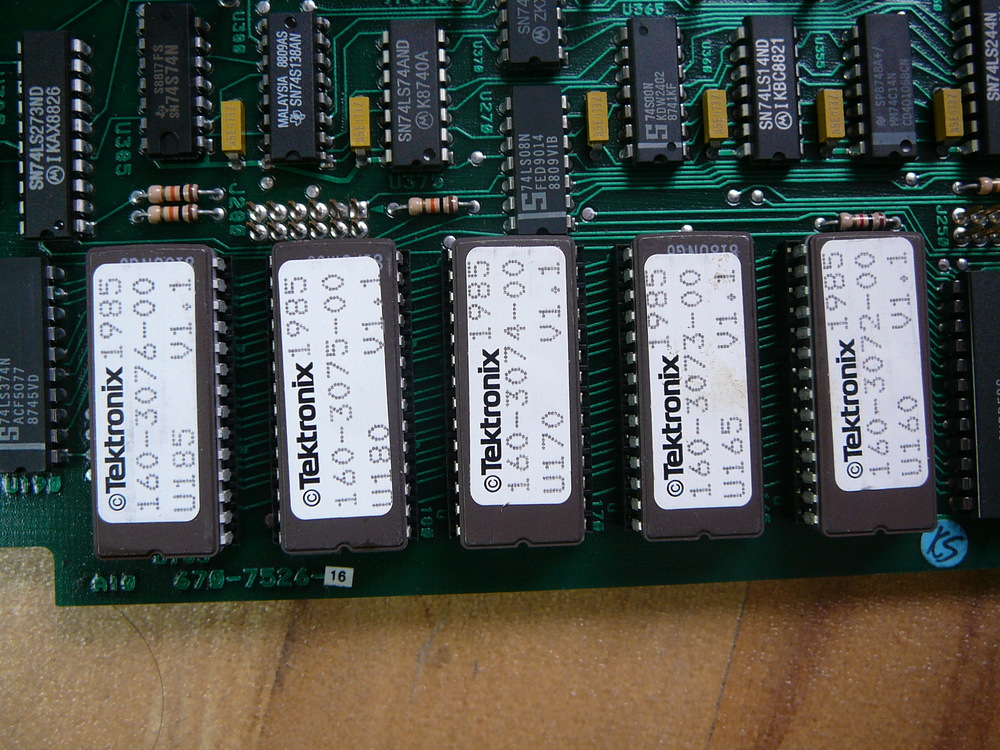

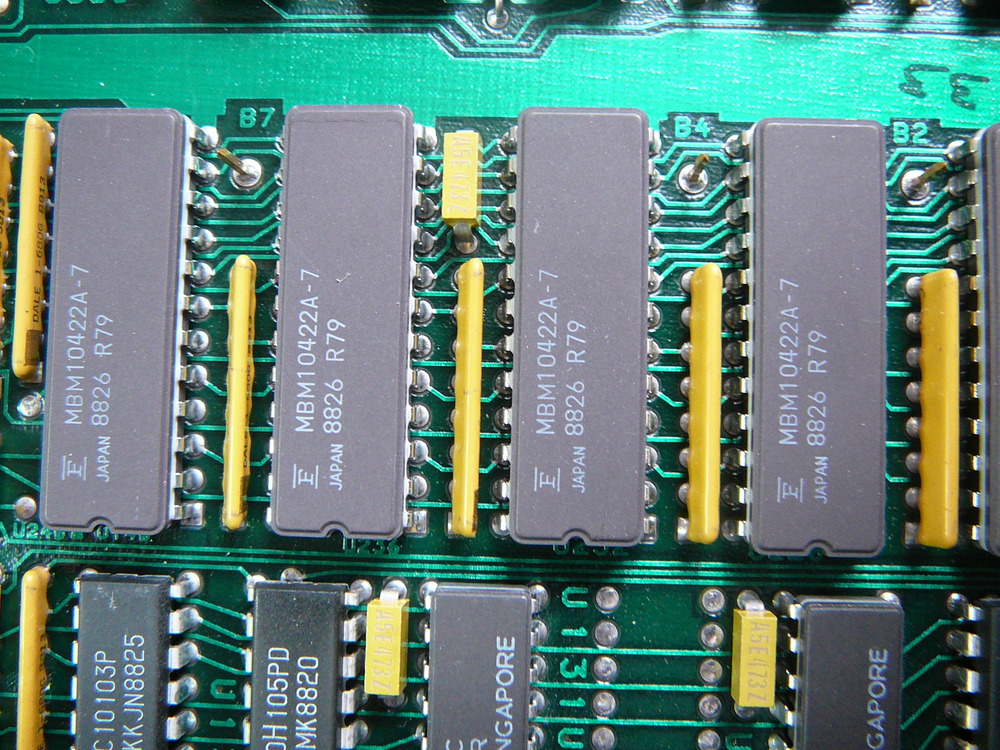

EPROMs auf der I/O Karte

EPROMs auf der I/O Karte

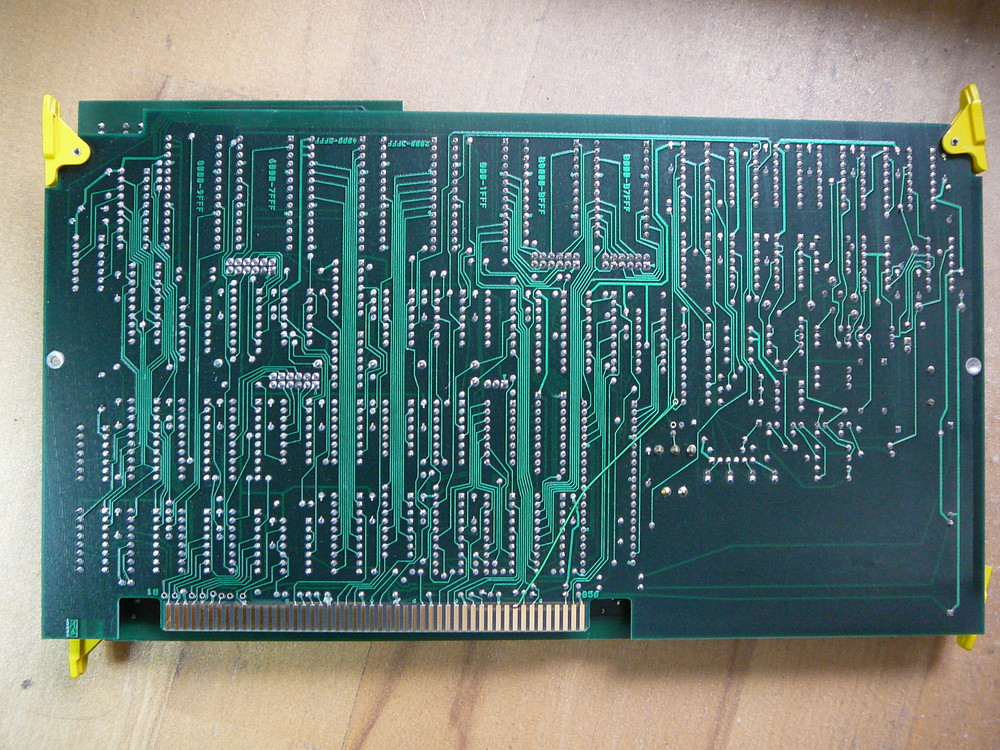

Rückseite I/O Karte

Rückseite I/O Karte

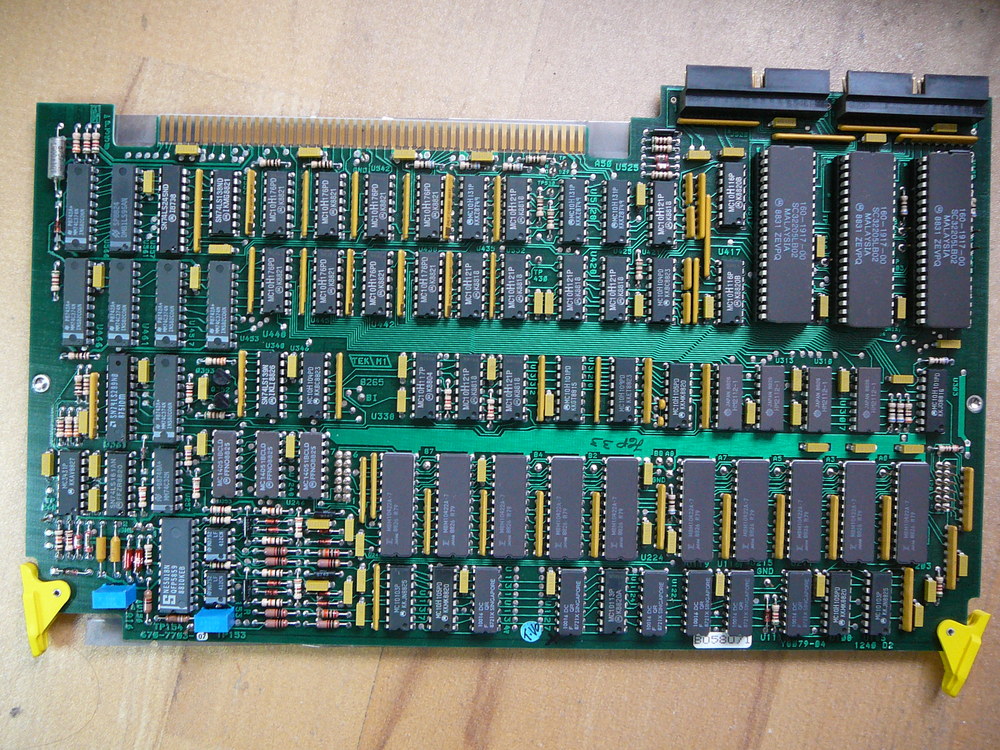

Die Display Karte

EPROMs auf der Display Karte

EPROMs auf der Display Karte

Rückseite Display Karte

Rückseite Display Karte

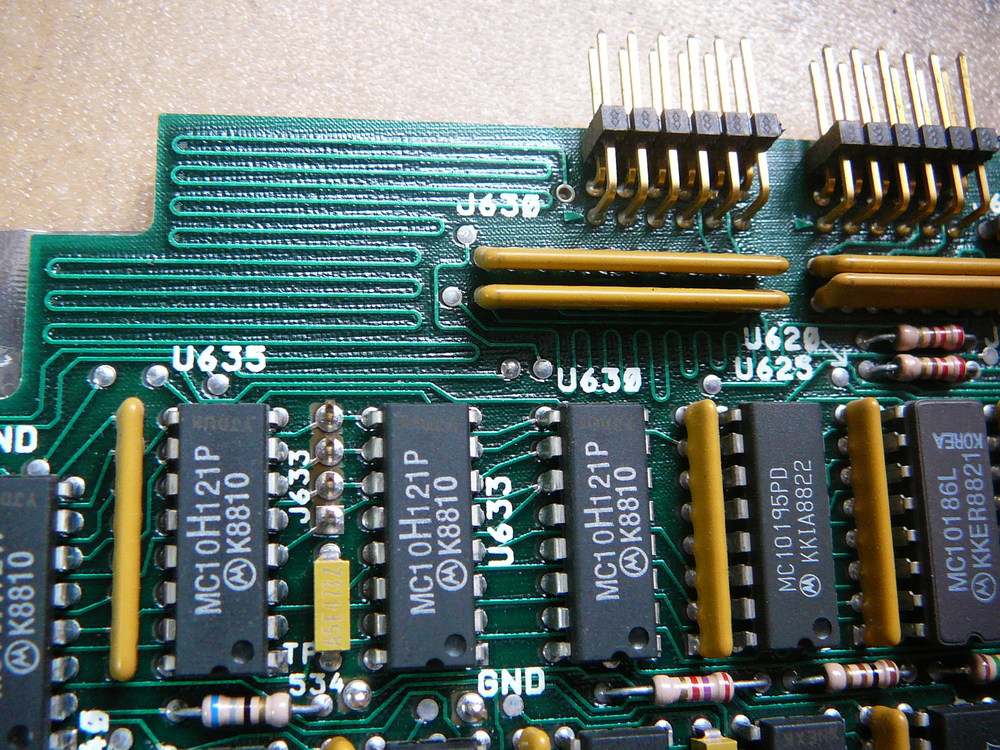

Die 18 Kanal Karte

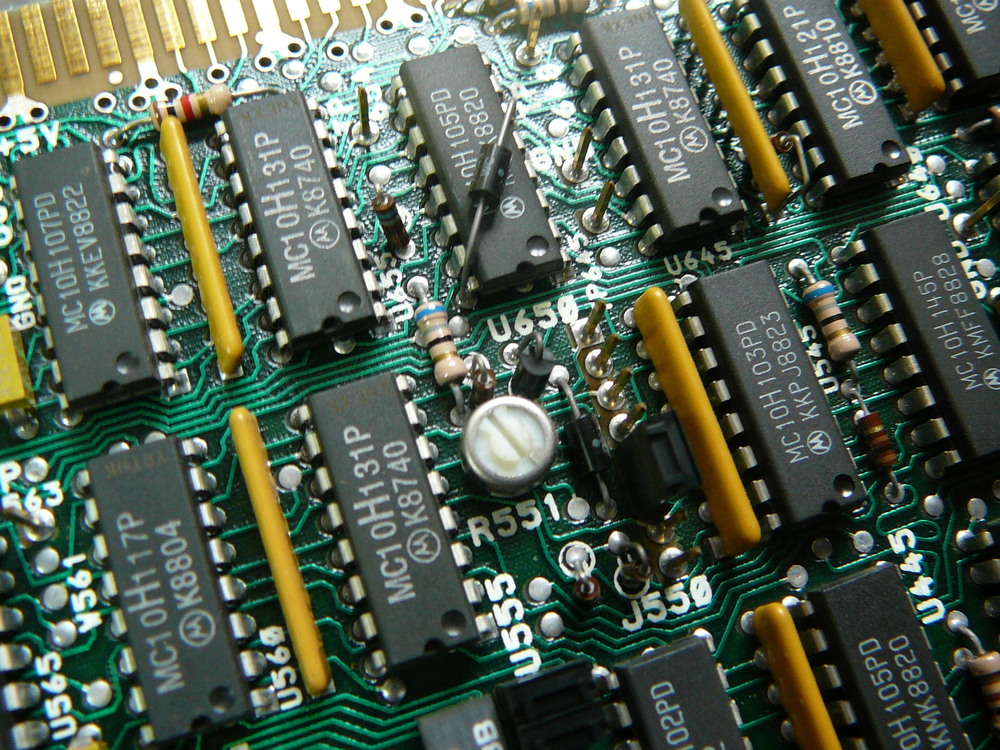

Eingangsbausteine

Eingangsbausteine

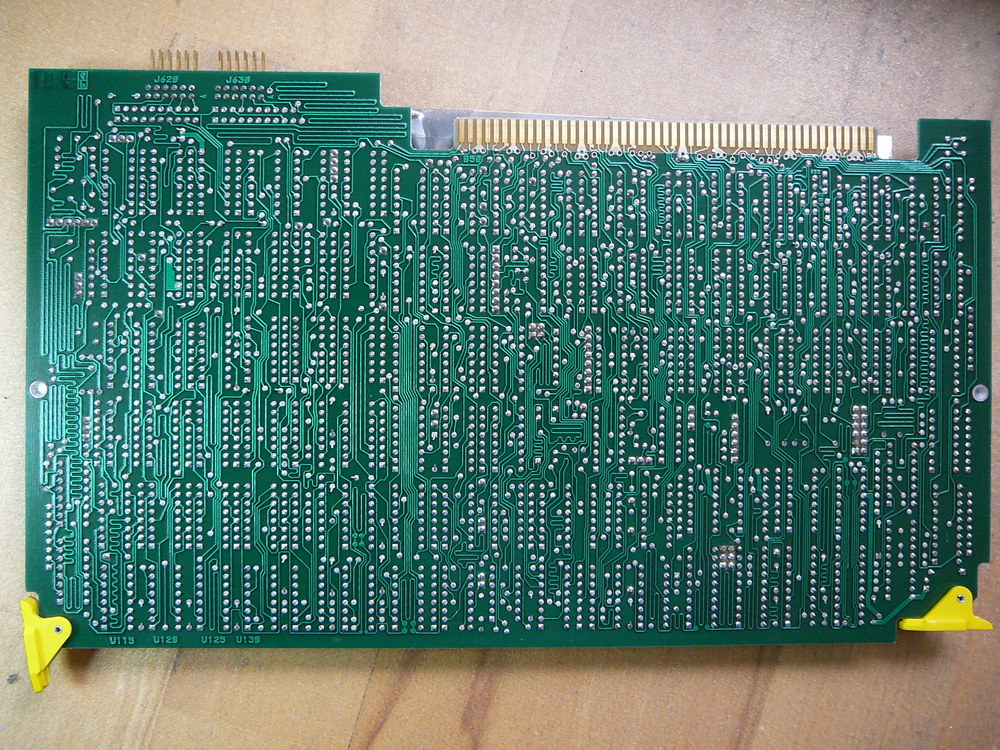

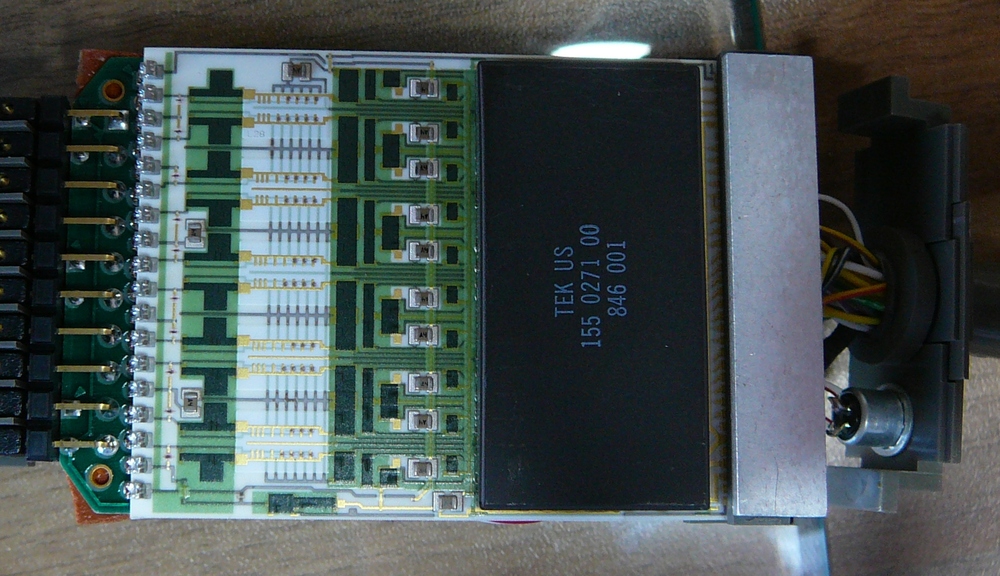

Rückseite 18 Kanal Karte

Rückseite 18 Kanal Karte

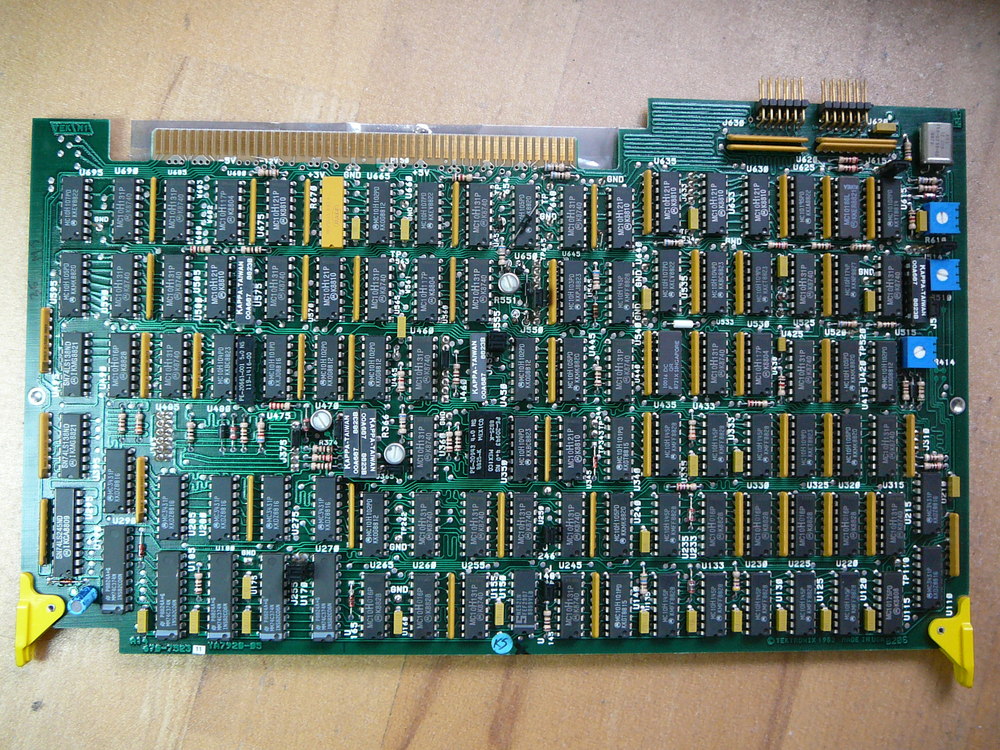

Die 9 Kanal Karte

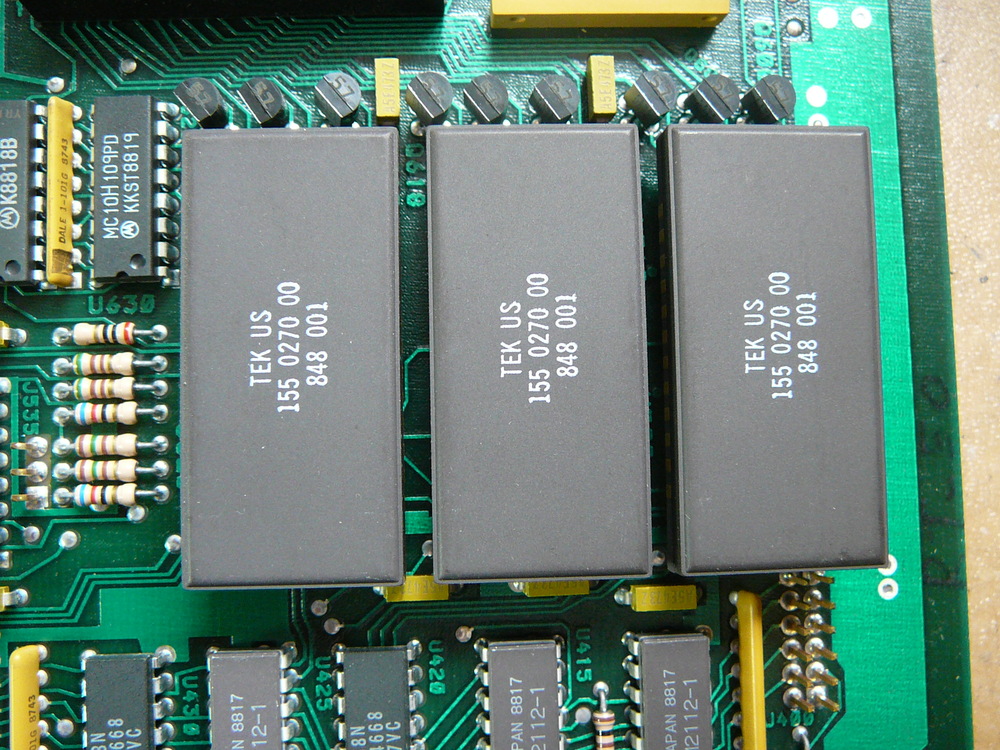

Tektronix Custom Chips

Tektronix Custom Chips

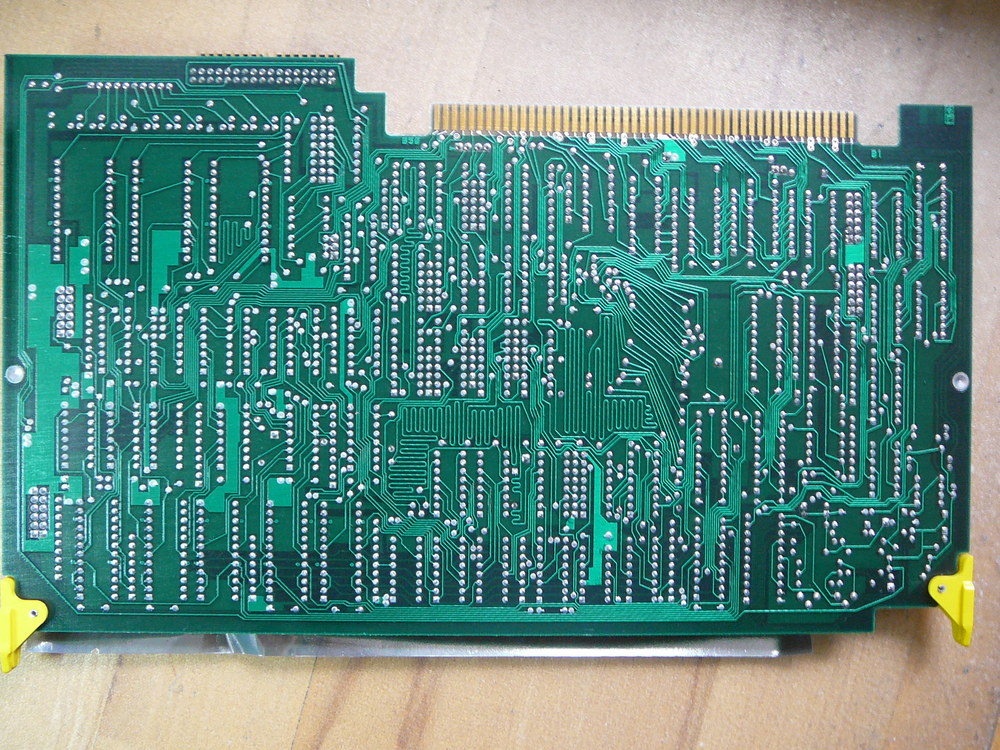

Rückseite 9 Kanal Karte

Rückseite 9 Kanal Karte

Die Trigger Karte

Rückseite Trigger Karte

Rückseite Trigger Karte

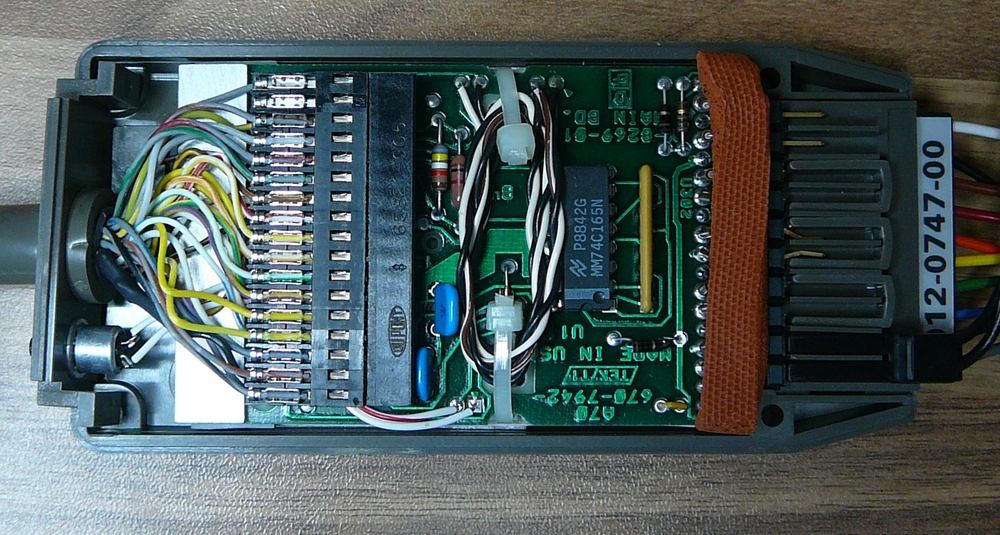

Pod 6460

Im folgenden einige Bilder einer geöffneten Pod 6460. Diese Probe hat 9 Dateneingänge sowie einen Clock/Qualifier-Eingang für synchronen Betrieb. Zur Pod gehören “Lead Sets” unterschiedlicher Ausführung, um die Pod an das Gerät unter Test anzuschließen. Die Lead Sets haben z.B. Mini-Krokodilklemmen. Es gibt auch spezielle Diagnostic Lead-Sets zum Anschluß an den eingebauten Test Pattern Generator des Tek1241.

Die Pod 6460 erlaubt die Einstellung des Thresholds für die Differenzierung von HIGH und LOW vom Tek 1241 aus.

geschlossene Pod

geschlossene Pod

Pod von oben

Pod von oben

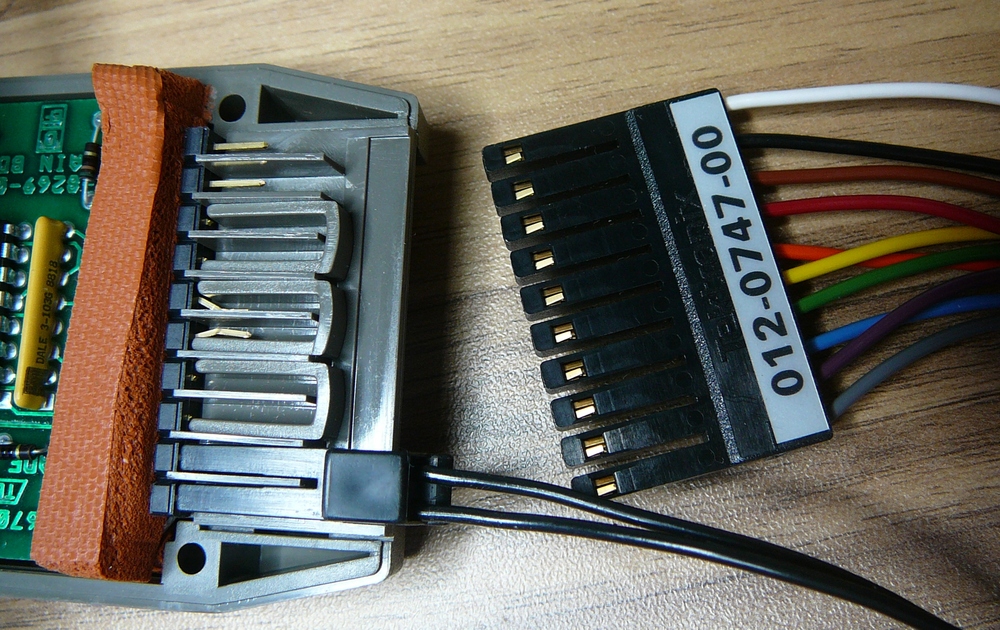

Das Lead Set (rechts) und die Verbindung zur Pod

Das Lead Set (rechts) und die Verbindung zur Pod

Geöffnete Pod von unten. Rechts ein größerer Custom

Chip von Tektronix.

Geöffnete Pod von unten. Rechts ein größerer Custom

Chip von Tektronix.

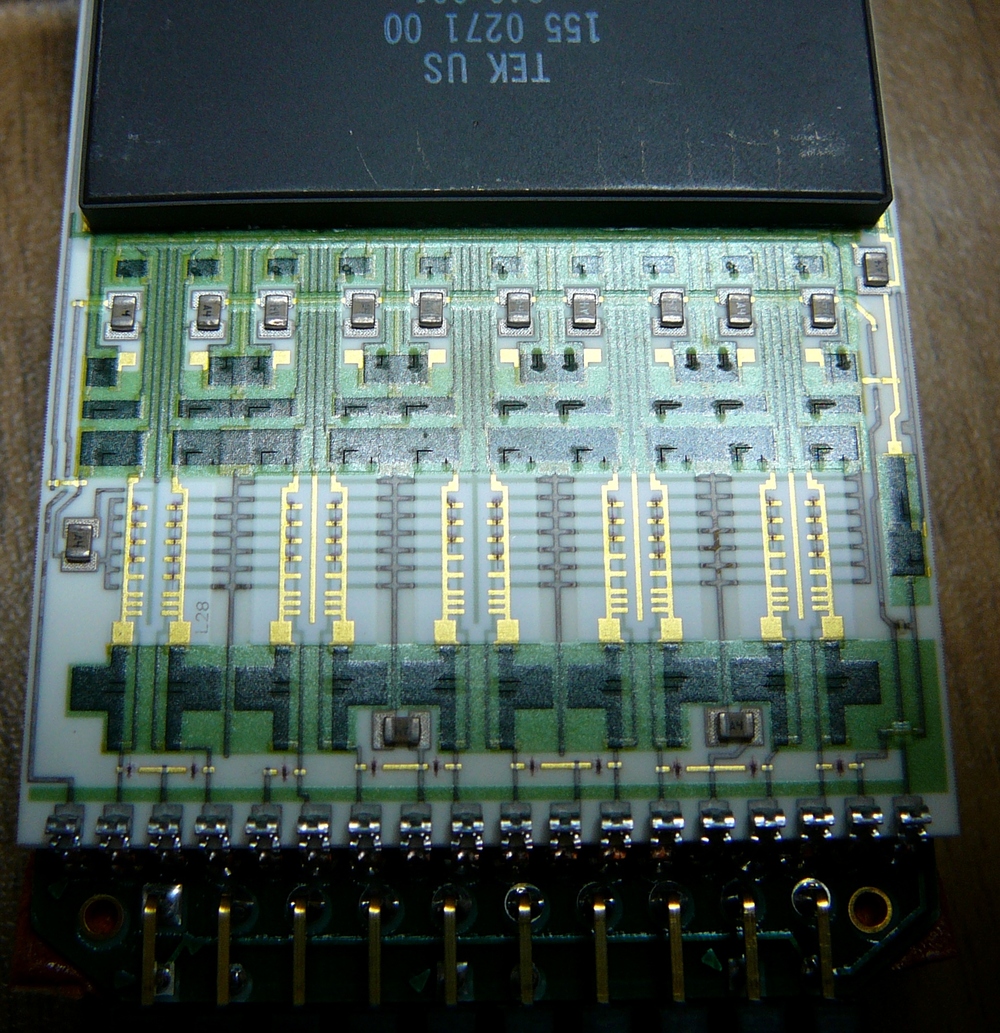

Bei dieser Platine (auf Keramik aufgebaut?) handelt

es sich vermutlich um einen komplexeren Attentuator für 9+1 Kanäle, um die

variablen Thresholds einzustellen.

Bei dieser Platine (auf Keramik aufgebaut?) handelt

es sich vermutlich um einen komplexeren Attentuator für 9+1 Kanäle, um die

variablen Thresholds einzustellen.

Stecker Richtung Tek1241, 2x17 polig

Stecker Richtung Tek1241, 2x17 polig

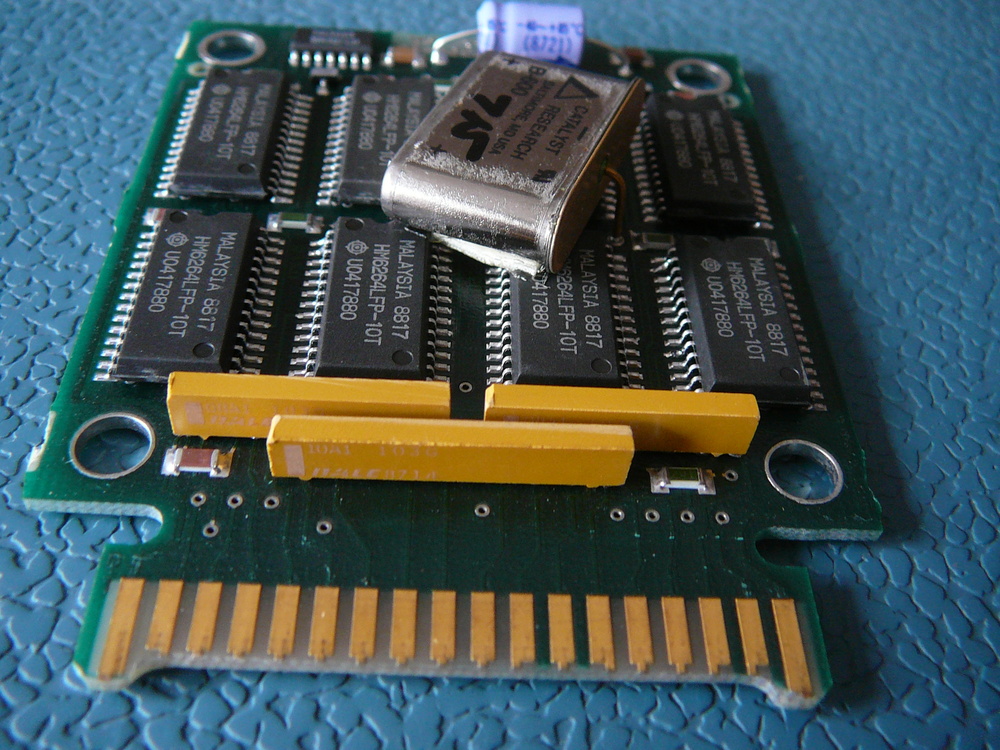

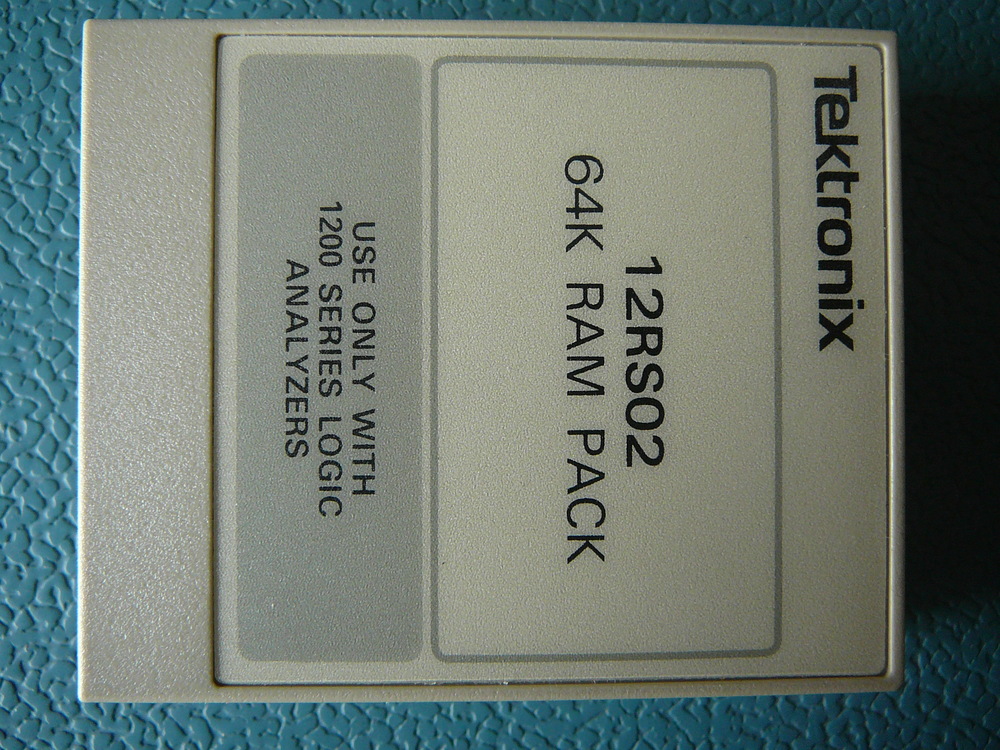

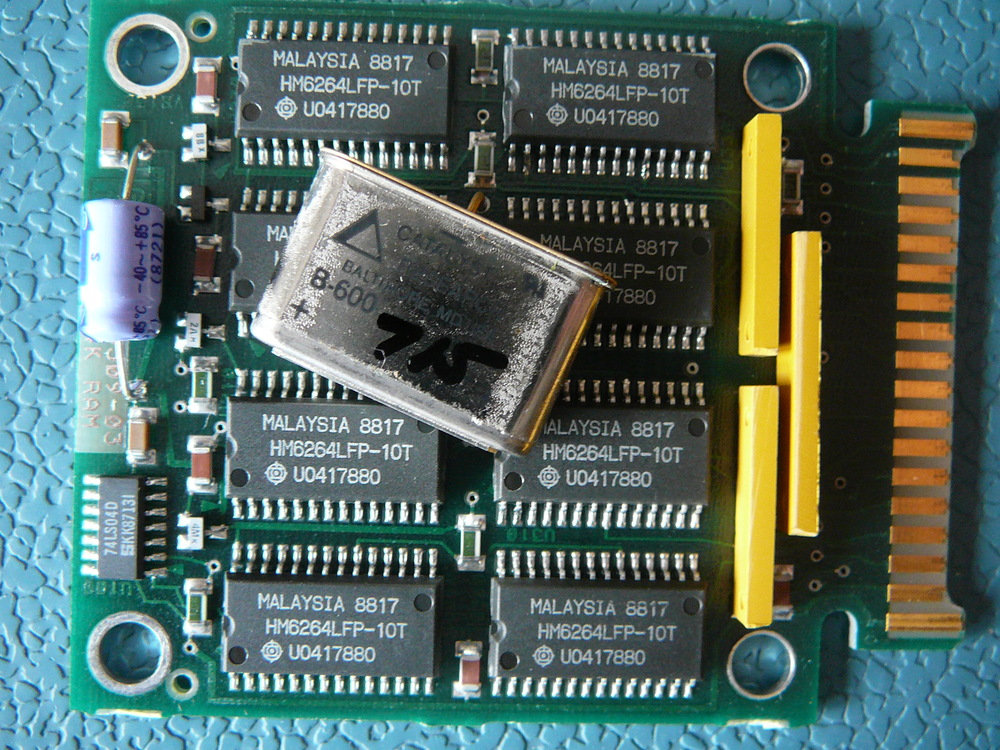

64KByte RAM Pack 12RS02

Auch hier besorgt die “Catalyst Research B-600” die

Langzeit-Spannungsversorgung der RAMs.

Auch hier besorgt die “Catalyst Research B-600” die

Langzeit-Spannungsversorgung der RAMs.